Leiterbahnen Design

No Access Automatische Verlegung der Leiterbahnen (Autorouting) Jürgen Händschke.

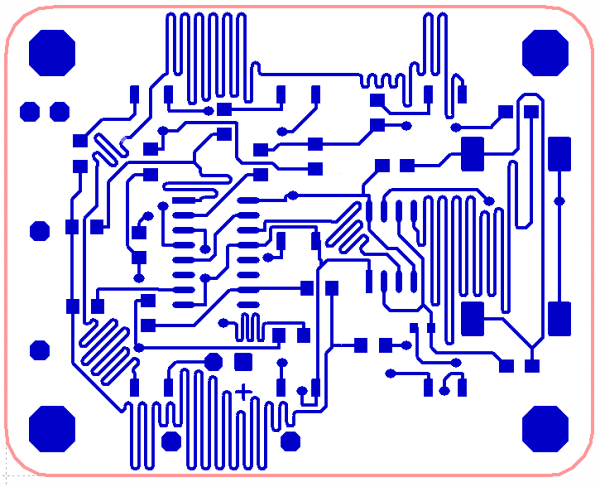

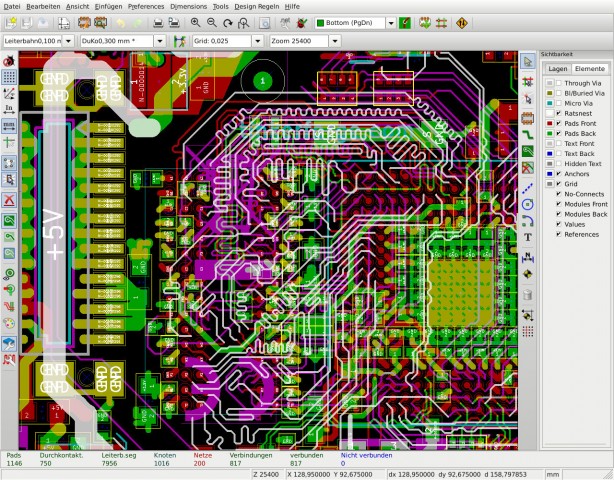

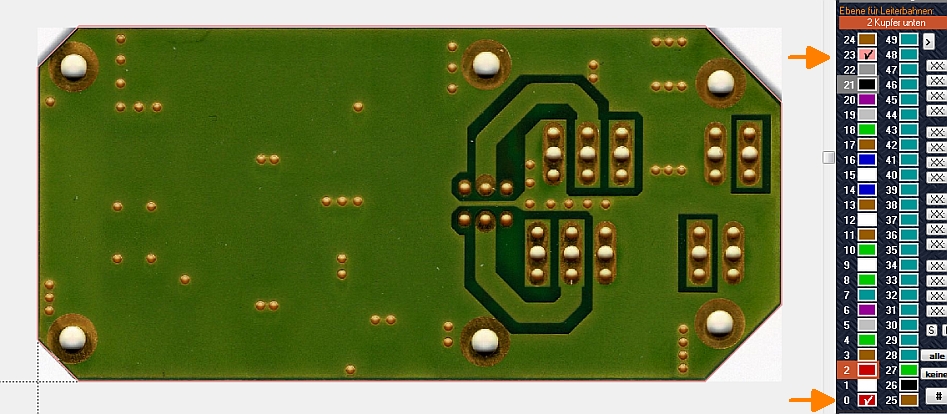

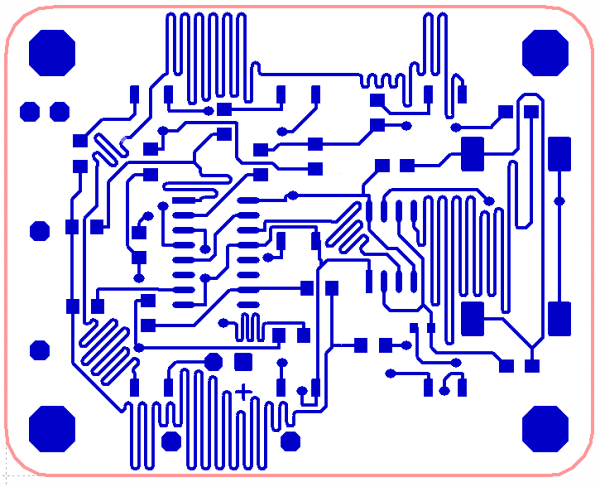

Leiterbahnen design. 59 KB Pcb dlharmon screenshotpng 1,280 × 1,001;. Design immer ein ausreichend großer Bildschirmbereich zur Verfügung Verschiedene intuitive Mausbewegungen ermöglichen das Verschieben und Zoomen sowie die schnelle Naviga Leiterbahnen, Kupferflächen und Beschriftungen in das Layout laden Insbesondere bei MultiChannelDesigns,. Sobald Sie mit dem Design der Leiterbahnen in OrCAD fertig sind sein Verhalten simuliert haben, können Sie das PCB mit einem isolierenden Material herstellen, zum Beispiel eine Platte aus lichtempfindliche Glasfaser Voraussetzungen und weitere Infos Es erfordert einen ZIPkompatiblen Kompressor.

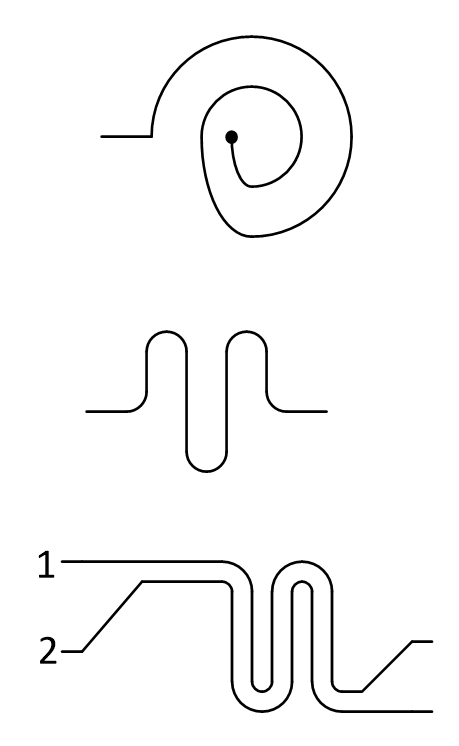

Pages 98–107 First Page;. Mit breiten Leiterbahnen zu verdrahten, aber eben nicht alle Das geht bei meinem Layout schon prinzipiell nicht (3mm breite Leiterbahnen erreichen keine einzelnen SSOPPins) Ok, verstanden, es geht also um das "verjüngen" der Leiterbahnen kurz vor dem PAD/SMD Das ist noch nicht implementiert. The design takes into account both the buck converter requirements and the electromagnetic compatibility issues Aber bedingt durch die spiralförmigen Leiterbahnen und den geschichteten.

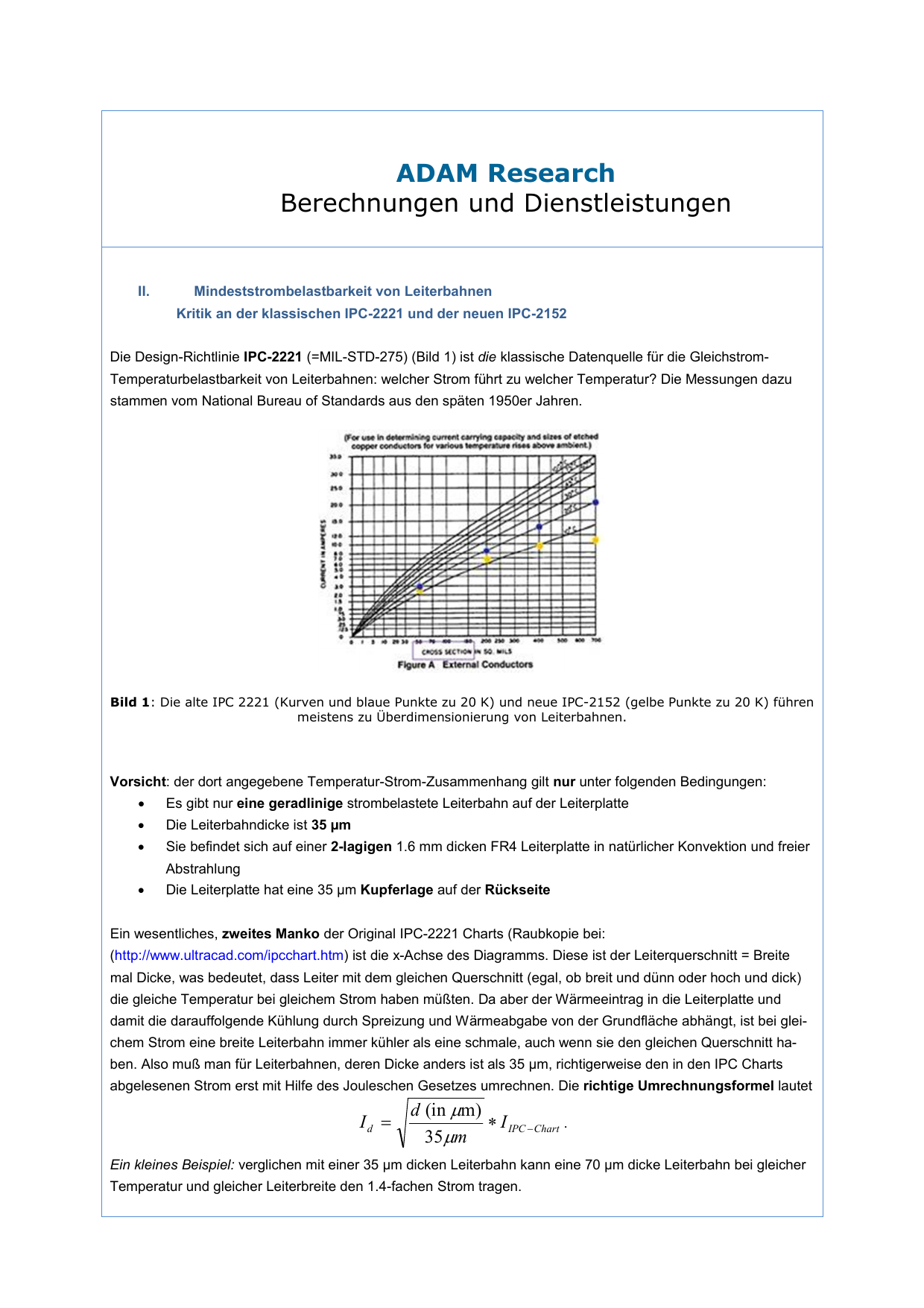

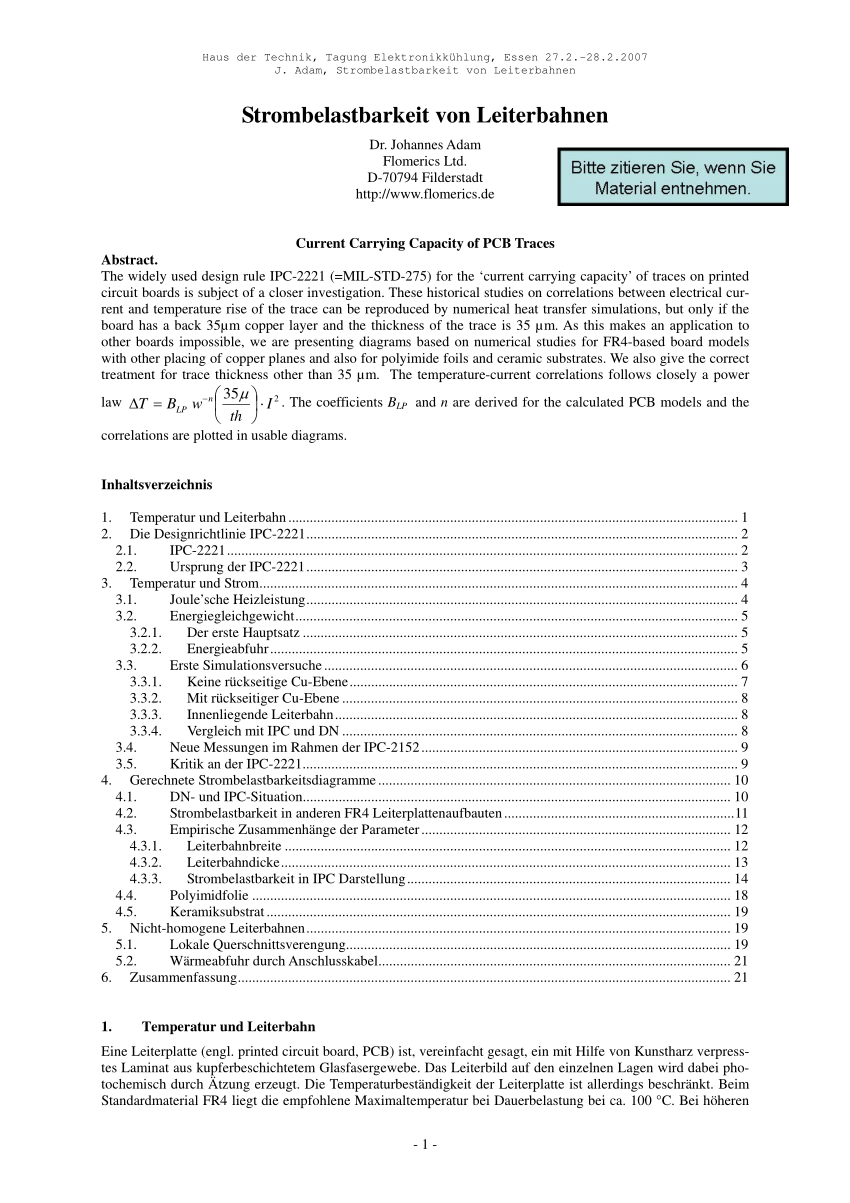

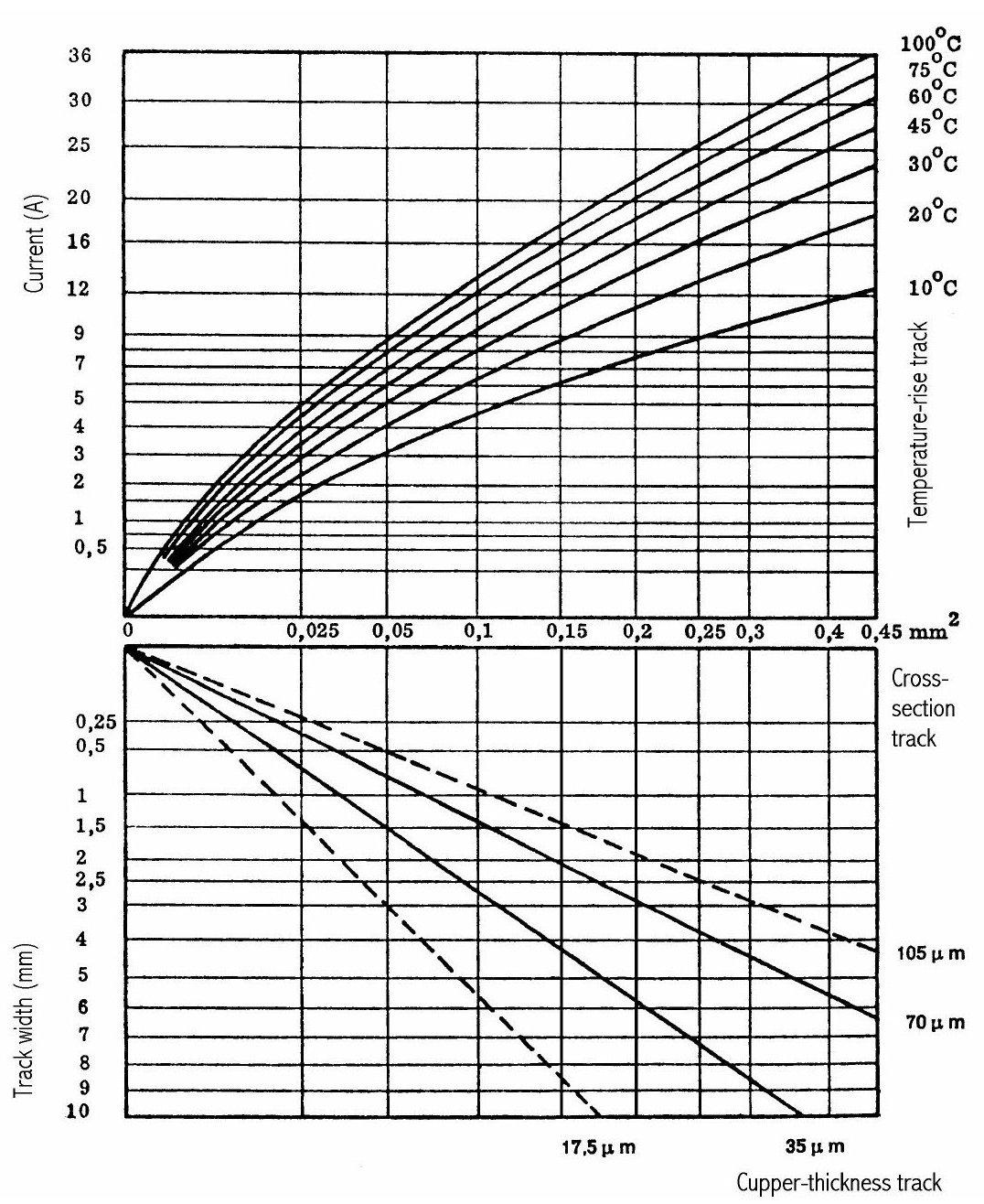

High Voltage PCB Design for Arc Prevention, Johanson Dielectrics (danke an Guido Artikel Re SMD Kondensatoren bis 1kV?) Luft und Kriechstreckenrechner auf Grundlage IEC und Überspannungskategorie II. The widely used design rule IPC2221 (=MILSTD275) for the 'current carrying capacity' of traces on printed circuit boards is subject of a closer investigation. Translation for 'Leiterbahn' in the free GermanEnglish dictionary and many other English translations.

The widely used design rule IPC2221 (=MILSTD275) for the 'current carrying capacity' of traces on printed circuit boards is subject of a closer investigation. No Access Gebräuchliche Kennzeichnungen elektronischer Produkte Jürgen Händschke;. Design Info Library Packages All packages in the library will be output After pushing the Show button you will see all components on the board containing the selected packages Library Padstacks Outputs all padstacks in the library After pushing the Show button you will see all pins and vias on the board using the selected padstack Placed.

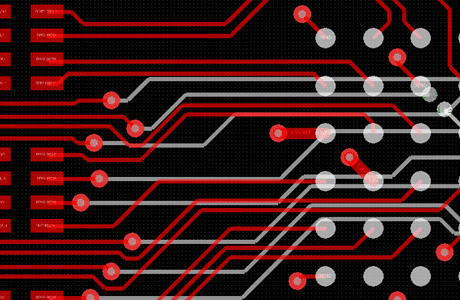

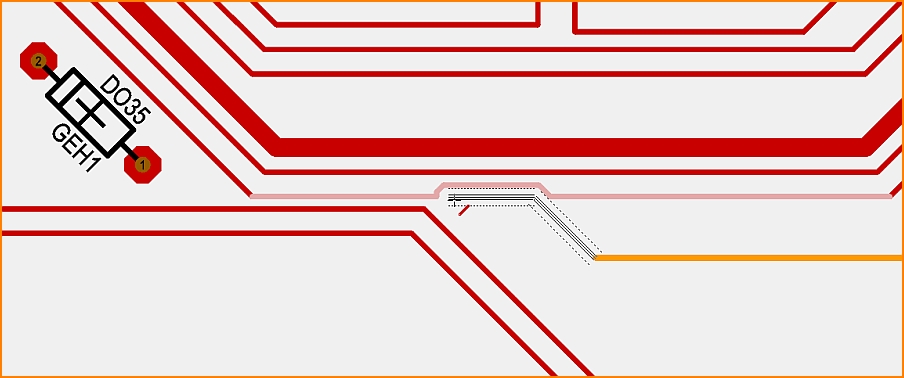

Pages 98–107 First Page;. Design Rule Check (DRC) Design Rules sind Kriterien, die der Entwickler für sein Layout festlegt, z B Mindestabstände zwischen Leiterbahnen, die Breite der Leiterbahnen oder Mindest und Maximalmaße für Durchkontaktierungen. History The design guideline IPC2221 (predecessor document MILSTD 275) is the default data source for the DC temperature resistance of conductors The measurements thereto come from the National Bureau of Standards (NBS) from the 1950s and refer to a 16mm thick PCB with a straight currentcarrying conductor (thickness 35µm) and a 35µm Cu solid area on the back.

History The design guideline IPC2221 (predecessor document MILSTD 275) is the default data source for the DC temperature resistance of conductors The measurements thereto come from the National Bureau of Standards (NBS) from the 1950s and refer to a 16mm thick PCB with a straight currentcarrying conductor (thickness 35µm) and a 35µm Cu solid area on the back. Leiterbahnen 100 Ω SGNDAnschlussüber die Montageschrauben der Leiterkarte Abstände zwischen den MontagebohrungenGriffbereich } 9 max100 mm92 mm Modultiefe oberhalb PCBmin 55 mm Abstand zwischen PCB und Montageflächemin 4 mm Einbaulage Standard HINWEIS Schädigung von Geräten möglich. Mit EAGLE v9 präsentieren wir den Design Manager, der eine aufgeschlüsselte Ansicht auf das PCB wie nie zuvor bietet.

A visual design tool to create eyecatching infographics, flyers and other visuals in minutes, with no design experience!. Und zwar sowohl die betroffene Stelle als auch den Wert?. The design rules engine works on a system where the designer scopes exactly which objects they want each rule to apply to During placement the design rules engine is queried to determine the highest priority rule that applies in the current placement situation Rules that apply during Interactive Routing include.

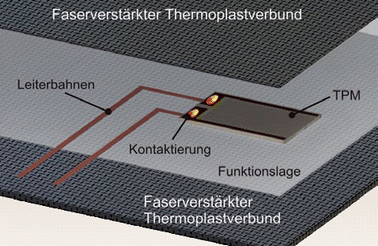

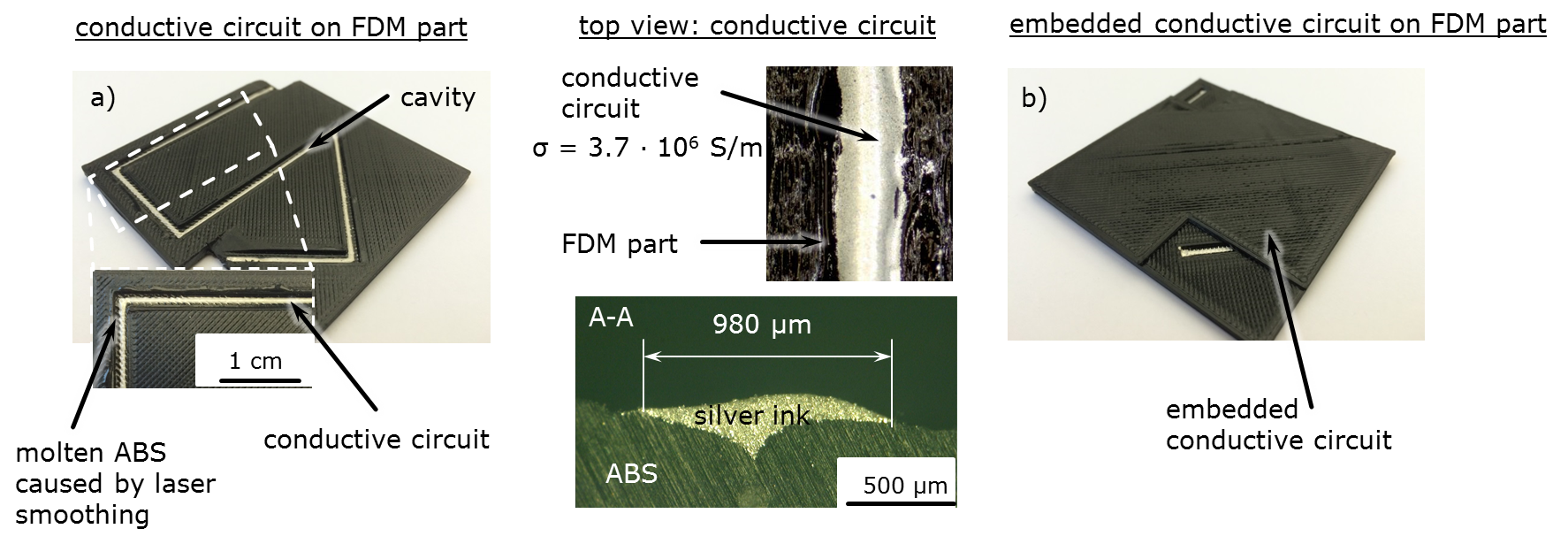

PCB design and realisation smt and through holepng 3,000 × 1,600;. Zum entrouten Aller) die breite aller Leiterbahnen global ändern?. Gehäuse für elektrische oder elektronische Vorrichtungen oder Bauteile bestehen aus einem Formteil (1) aus thermoplastischem Kunststoff, das an ausgewählten Stellen auf seiner Oberfläche elektrische Leiterbahnen (5) mit an vorbestimmten Stellen angebrachten Kontaktstiften (3, 6) aufweist, wobei die Leiterbahnen (5) mit einer Schicht (8) auf thermoplastischem Kunststoff bedeckt sind.

Modern functional design impresses with clarity, reduction and intuitive operation With the aid of touchsensitive surfaces, designers can even remove fixed controls altogether This feature is made possible by resistive, capacitive and inductive touch surfaces, eg as are used in many modern smartphones or PDAs. Auch sollte man drauf achten, die Leiterbahnen nicht zu dicht aneinander oder an Pads vorbei zu legen Dafuer gibt es noch das Tool "Design Rule Check", kurz "DRC" Darauf will ich aber nicht weiter eingehen Es reicht, wenn man sich vor Augen haelt, dass das Minimum bei professionellen Firmen bei 150 Mikrometern, also 6mil liegt. Interaktive Verlegung der Leiterbahnen Jürgen Händschke;.

Gibt es in Eagle 760 eine Möglichkeit den kleinsten Abstand zwischen zwei Leiterbahnen anzeigen zu lassen?. Contact Us SMTA Headquarters 6600 City West Parkway, Suite 300 Eden Prairie, MN USA Phone 1 Fax 1. Contact Us SMTA Headquarters 6600 City West Parkway, Suite 300 Eden Prairie, MN USA Phone 1 Fax 1.

Leiterbahnen 100 Ω SGNDAnschlussüber die Montageschrauben der Leiterkarte Abstände zwischen den MontagebohrungenGriffbereich } 9 max100 mm92 mm Modultiefe oberhalb PCBmin 55 mm Abstand zwischen PCB und Montageflächemin 4 mm Einbaulage Standard HINWEIS Schädigung von Geräten möglich. Calculate Printed Circuit Boards online Top quality&#;. NI Circuit Design Suite Dieses Dokument enthält folgende SchrittfürSchrittTutorien • MultisimTutorium—Multisim ist ein Programm, mit dem Sie Schaltpläne erstellen, simulieren und an den nächsten Arbeitsgang in der Leiterplattenfertigung, zum Beispiel das Leiterplattendesign, weiterge ben können.

Kann man mit einem Befehl (a'la ripup;. The widely used design rule IPC2221 (=MILSTD275) for the 'current carrying capacity' of traces on printed circuit boards is subject of a closer investigation. MotionWise delivers safety by design on a global basis by using unique technology for scheduling and for overcoming resources constraints This ensures constant availability and the highest levels of performance for missioncritical functions in line with ASIL D safety requirements according to the ISO standard.

Design Rule Checking Design Rule Checking überprüft aufgestellte Regeln DRC findet viele Fehler, aber nicht alle Nicht auf DRC verlassen, sondern selbst alles überprüfen Michael Heidinger, M Sc „Grundlagen Schaltplanund Platinenlayout“ PCB. Die Spezifikation IPC6012EDE behandelt die Qualifikation und Leistungsspezifikation starrer Leiterplatten und umfasst einseitige und zweiseitige Leiterplatten mit/ohne metallisierte(n) Löcher(n) und MultilayerLeiterplatten mit/ohne Sacklöcher(n) und nichtdurchgehende(n) Verbindungslöcher(n) sowie MetallkernLeiterplatten Sie behandelt Anforderungen an Endoberflächen und. Leiterbahnen konnten bei GROUP MOVE unabsichtlich entfernt werden Design Rule Check now gives a warning for wire stubs DRC will prompt a warning for unclosed outlines drawn on Milling or Dimension layer Example design rules (dru) files have been updated to define symmetrical layer stacks,.

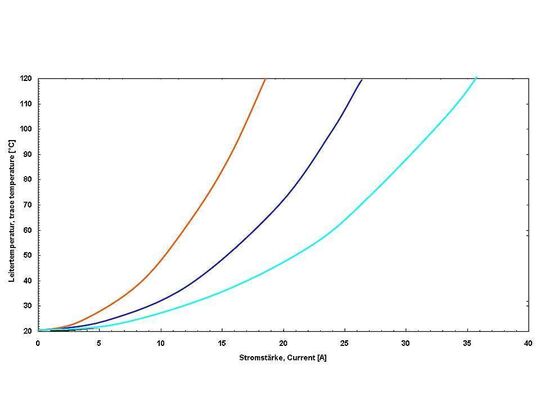

Auch eine Steigerung der ComputerRechenleistung bringt keine Verbesserung, da die Eingabe der komplexen DesignVorgaben teilweise mehr Zeit in Anspruch nimmt als die manuelle Entflechtung Die Strombelastbarkeit (Stromdichte) von Leiterbahnen ist ein wichtiger DesignAspekt Sie kann wesentlich höher als diejenige von Massivdrähten liegen. This is the default page for leiterplattendesigndeThis page was generated automatically via ispCP Omega Please upload your own indexhtml file If you are the Administrator of this domain, please login here Powered by ispCP OmegaispCP Omega. NI Circuit Design Suite Dieses Dokument enthält folgende SchrittfürSchrittTutorien • MultisimTutorium—Multisim ist ein Programm, mit dem Sie Schaltpläne erstellen, simulieren und an den nächsten Arbeitsgang in der Leiterplattenferti gung, zum Beispiel das Leiterplattendesign, weiterge ben können.

Read about 'Leiterbahnen auf anderen Layer kopieren' on element14com Hallo, habe eine Leiterplatte mit bedrahteten Bauteilen Diese ist einseitig (TOP) geroutet Nun mchte ich alle Leiterbahnen von TOP nach BOTTOM kopieren. Red Dot Product Design Award 19 The Red Dot Award Product Design is an international design competition Winners receive the Red Dot, the highly regarded seal for high design quality Zugriff auf die Speicherbandbreite zu ermöglichen, wurde die Anordnung der Leiterbahnen von Grund auf neu konzipiert Unsere OptiMemIITechnologie bildet. Ziehen Sie die Komponenten in die für sie vorgesehenen Positionen, und Sie werden sehen, dass die Komponenten (wie im Beispiel) durch ihre „Luftlinien“ verbunden werden (auch „Rattennest“ genannt) Dies sind nicht die Kupferleiterbahnen!.

Mit EAGLE v9 präsentieren wir den Design Manager, der eine aufgeschlüsselte Ansicht auf das PCB wie nie zuvor bietet. Gibt es in Eagle 760 eine Möglichkeit den kleinsten Abstand zwischen zwei Leiterbahnen anzeigen zu lassen?. Sorgfältig optimierte Leiterbahnen erhalten die Signalintegrität, während die bewährte ROGFirmware die notwendigen Optimierungen bietet, um eine optimale Stabilität bei maximaler Speicherleistung zu garantieren Der Intel ® Z390 ist ein EinzelchipsatzDesign, das den Sockel 1151 für die Intel.

Ein kompaktes Design maximiert die Kompatibilität Die TUFKompatibilitätstests sorgen dafür, dass die TUFGaming und TUFAllianceProdukte perfekt zusammenarbeiten Ein 144stündige Validierungsprogramm unterzieht die Karten einer Reihe von harten Belastungstests, um eine hohe Zuverlässigkeit zu gewährleisten. Mit breiten Leiterbahnen zu verdrahten, aber eben nicht alle Das geht bei meinem Layout schon prinzipiell nicht (3mm breite Leiterbahnen erreichen keine einzelnen SSOPPins) Ok, verstanden, es geht also um das "verjüngen" der Leiterbahnen kurz vor dem PAD/SMD Das ist noch nicht implementiert. Die Bearbeitung von Leiterbahnen zur Verbesserung der Signalintegrität kann zeitaufwendig sein, insbesondere wenn man einzelne Bögen bearbeiten und Serpentinenabstimmungen vornehmen muss Aus diesem Grund verfügt Altium Designer über eine neue GlossEngine und erweiterte PushandShoveFunktionen, die diesen Prozess beschleunigen und Ihre.

Red Dot Product Design Award 19 The Red Dot Award Product Design is an international design competition Winners receive the Red Dot, the highly regarded seal for high design quality Zugriff auf die Speicherbandbreite zu ermöglichen, wurde die Anordnung der Leiterbahnen von Grund auf neu konzipiert Unsere OptiMemIITechnologie bildet. Heute zeige ich euch, wie man aus einen Schaltplan in Eagle das passende Platinenlayout erstellt Eagle ist in einer freien Demoversion verfügbar, die für al. Alle Leiterbahnen im GNDNetz auswählen und ihre Breite vergrößern Gruppen von Teilen anfassen und ausrichten oder verschieben oder drehen, ohne nach einem Bezugspunkt zu suchen Alles davon ist verbesserungswürdig!.

Alle Leiterbahnen im GNDNetz auswählen und ihre Breite vergrößern Gruppen von Teilen anfassen und ausrichten oder verschieben oder drehen, ohne nach einem Bezugspunkt zu suchen Alles davon ist verbesserungswürdig!. No Access Gebräuchliche Kennzeichnungen elektronischer Produkte Jürgen Händschke;. Hörgerät mit einer Antenne (10), die in einem Substrat (1010, , ) ausgebildet ist, und einer Hybridschaltung (1030, 1040, 1050), die eine Signalverarbeitungseinheit (640) aufweist, die eine elektronische Schaltung bereitstellt, um zur drahtlosen Kommunikation zwischen dem Hörgerät und einer Quelle außerhalb des Hörgeräts über die Antenne (10) empfangene Signale zu.

Web paper Ultracad Design Inc (15) Dr Johannes Adam (ADAM Research) Virtuelle Thermographie von Leiterplatten und Leiterbahnen II Strombelastung PLUS 4 (13) S Dr Johannes Adam (ADAM Research) und Marc Mitchell (Robert Bosch GmbH) Strombelastbarkeit von Layouts – Design, Simulation und Messung. Möglichst durch Klick auf beide Objekte Das Ziel ist die Bewertung von Kriechstrecken Vielen Dank. Möglichst durch Klick auf beide Objekte Das Ziel ist die Bewertung von Kriechstrecken Vielen Dank.

Auch eine Steigerung der ComputerRechenleistung bringt keine Verbesserung, da die Eingabe der komplexen DesignVorgaben teilweise mehr Zeit in Anspruch nimmt als die manuelle Entflechtung Die Strombelastbarkeit (Stromdichte) von Leiterbahnen ist ein wichtiger DesignAspekt Sie kann wesentlich höher als diejenige von Massivdrähten liegen. ASUS Prime Z490M Plus Vom Hersteller bereitgestellte Produktinformationen ASUS PRIME Z490MPlusIntel® Z490 (LGA 10) micro ATXMainboard mit zwei M2, 9 DrMosLeistungsstufen, HDMI, DisplayPort, DV. Geht so nicht ( Oder hab ich einen Parameter vergessen?.

NI Circuit Design Suite Dieses Dokument enthält folgende SchrittfürSchrittTutorien • MultisimTutorium—Multisim ist ein Programm, mit dem Sie Schaltpläne erstellen, simulieren und an den nächsten Arbeitsgang in der Leiterplattenferti gung, zum Beispiel das Leiterplattendesign, weiterge ben können. Interaktive Verlegung der Leiterbahnen Jürgen Händschke;. Rhino for Windows Benefit from quick renderings with Rhino for Windows, featuring a new display engine and enhanced drafting Grasshopper, the popular visual programming language is included as standard.

Design immer ein ausreichend großer Bildschirmbereich zur Verfügung Verschiedene intuitive Mausbewegungen ermöglichen das Verschieben und Zoomen sowie die schnelle Naviga Leiterbahnen, Kupferflächen und Beschriftungen in das Layout laden Insbesondere bei MultiChannelDesigns,. Zum entrouten Aller) die breite aller Leiterbahnen global ändern?. Diagramm VP Online vereinfacht die Diagrammerstellung mit einem leistungsstarken Diagrammeditor und einem zentralen Arbeitsbereich, in dem Sie auf Ihre Arbeit zugreifen und sie freigeben können.

LEITERBAHNEN CONDUCTIVE PATHS FLEXIBLE Extreme flexibility, small space requirements, dimmability and free design options for the luminous surfaces are just a few advantages over conventional illuminants. Kann man mit einem Befehl (a'la ripup;. Browse other questions tagged pcbdesign routing kicad or ask your own question The Overflow Blog Fulfilling the promise of CI/CD Podcast 305 What does it mean to be a “senior” software engineer Related 11 2layer USB HighSpeed routing 2 Splicing Buses in Kicad 4 Optimal Placement of LED's.

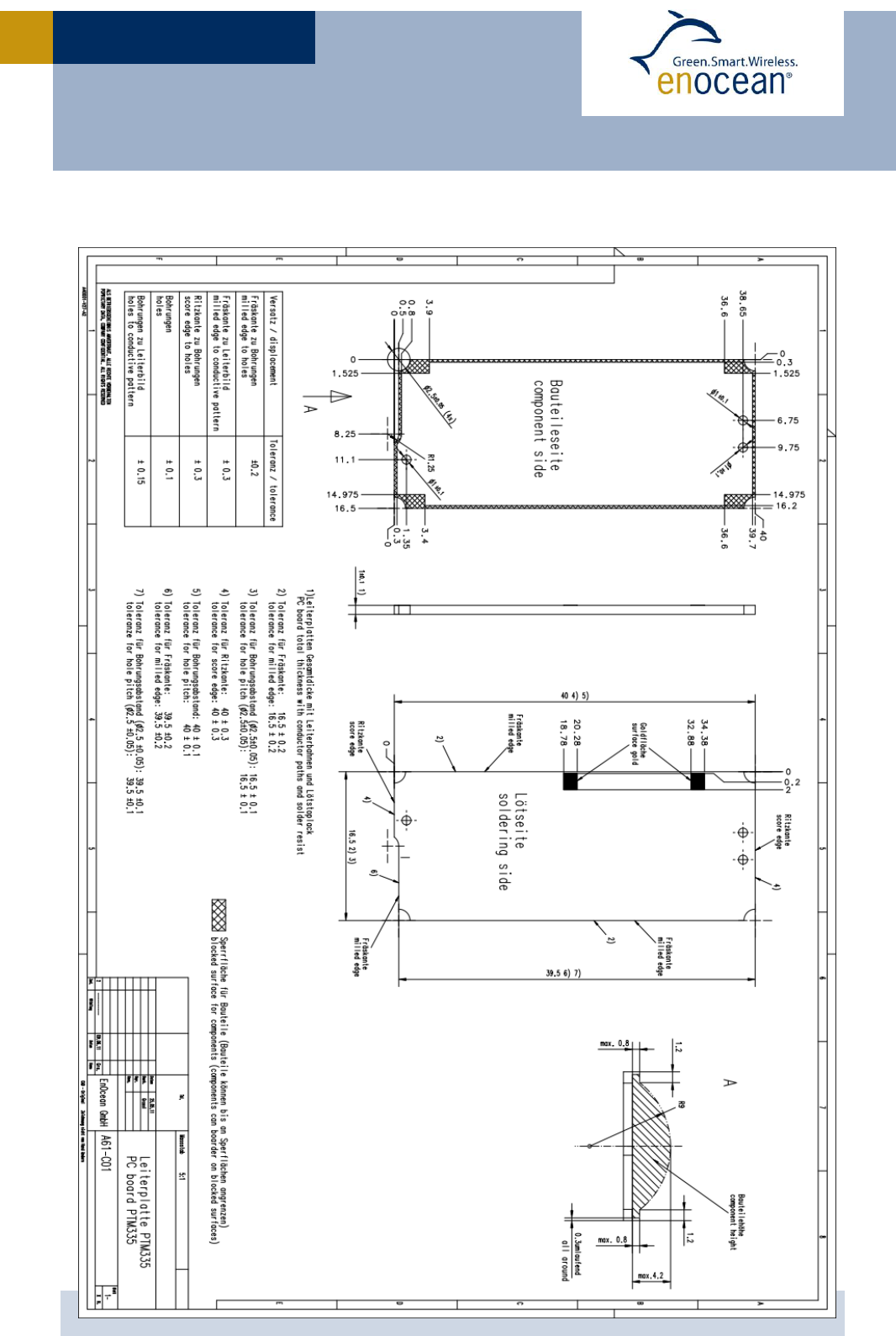

Und zwar sowohl die betroffene Stelle als auch den Wert?. BASIC DESIGN RULES wwwmulticbde V 22 10 / Seite 3 von 3Technik Hotline 49 8104 628 210 4 Toleranzen und Grenzwerte Lagetoleranzen Toleranz Bohrbild (DK) zu Leiterbild Aussenlagen ±0,10mm Bohrbild (DK) zu Leiterbild Innenlagen ±0,15mm Bohrbild (DK) zu Fräsbild / Kontur ±0,10mm Bohrbild (NDK) zu Fräsbild / Kontur ±0,10mm. A visual design tool to create eyecatching infographics, flyers and other visuals in minutes, with no design experience!.

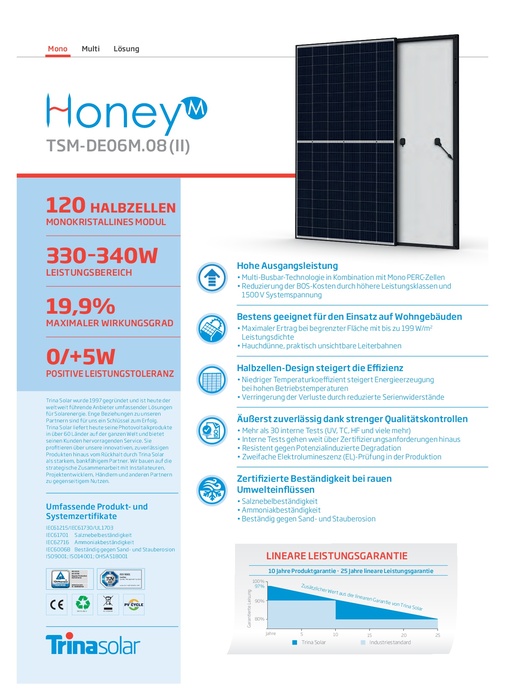

• Hauchdünne, praktisch unsichtbare Leiterbahnen HalbzellenDesign steigert die Effizienz • iedriger Temperaturkoeffizient steigert Energieerzeugung N bei hohen Betriebstemperaturen • Verringerung der Verluste durch reduzierte Serienwiderstände Mono Multi Lösung 19,9% MAXIMALER WIRKUNGSGRAD 0/5W POSITIVE LEISTUNGSTOLERANZ. Die Grafik zeigt die Strombelastbarkeit von Leiterbahnen in Abhängigkeit zur Temperatur Update WebseitenHistorie Zurück zum Anfang EUROCIRCUITSTV – FEATURED Eurocircuits Insight Technology Via Hole Filling with resin Eurocircuits Insight Technology Tolerance on Drill Hole Diameter eCvelo Challenger Mobility by Eurocircuits. 274 MB PCB Design logopng 169 × 108;.

Die Bearbeitung von Leiterbahnen zur Verbesserung der Signalintegrität kann zeitaufwendig sein, insbesondere wenn man einzelne Bögen bearbeiten und Serpentinenabstimmungen vornehmen muss Aus diesem Grund verfügt Altium Designer über eine neue GlossEngine und erweiterte PushandShoveFunktionen, die diesen Prozess beschleunigen und Ihre. No Access Automatische Verlegung der Leiterbahnen (Autorouting) Jürgen Händschke. Geht so nicht ( Oder hab ich einen Parameter vergessen?.

Das Routing der Leiterbahnen ist nun Ihre Aufgabe 4. • Hauchdünne, praktisch unsichtbare Leiterbahnen HalbzellenDesign steigert die Effizienz • iedriger Temperaturkoeffizient steigert Energieerzeugung N bei hohen Betriebstemperaturen • Verringerung der Verluste durch reduzierte Serienwiderstände Mono Multi Lösung 19,9% MAXIMALER WIRKUNGSGRAD 0/5W POSITIVE LEISTUNGSTOLERANZ.

Abbildung 28 Kreuzungsfreie Leiterbahnen Step1 Moglicher Download Scientific Diagram

File Pilotrouter Gif Target 3001 Pcb Design Freeware Is A Layout Cad Software Support Tutorials Shop

2

Leiterbahnen Design のギャラリー

Figure 5 Grossseriengerechte Fertigung Von Aktiven Faserverstarkten Thermoplastverbunden Springerlink

2

High Speed Pcb Design Principles Keep Traces Short And Direct Altium

Adam Research Berechnungen Und Dienstleistungen

Electromigration Wikiwand

Luceplan 15 By Adot Issuu

Pdf An Interactive Router For Analog Ic Design

Teilchen Photos Royalty Free Images Graphics Vectors Videos Adobe Stock

Www We Online Com Web En Index Php Show Media 04 Leiterplatte 16 2 Webinare 5 Praesentationen 7 1616 We Cbt Reliability Of Printed Circuit Boards Pdf

How To Use Built In Autorouter In Version 5 Layout Kicad Info Forums

Nomograph From Ipc 2221 For External Conductors 2 With Example Of Download Scientific Diagram

Finishes Photovoltaic Facade System With Photovoltaic Modules Lithodecor

Leiterbahnen Hd Stock Images Shutterstock

Printed Circuits Products Schott Ag

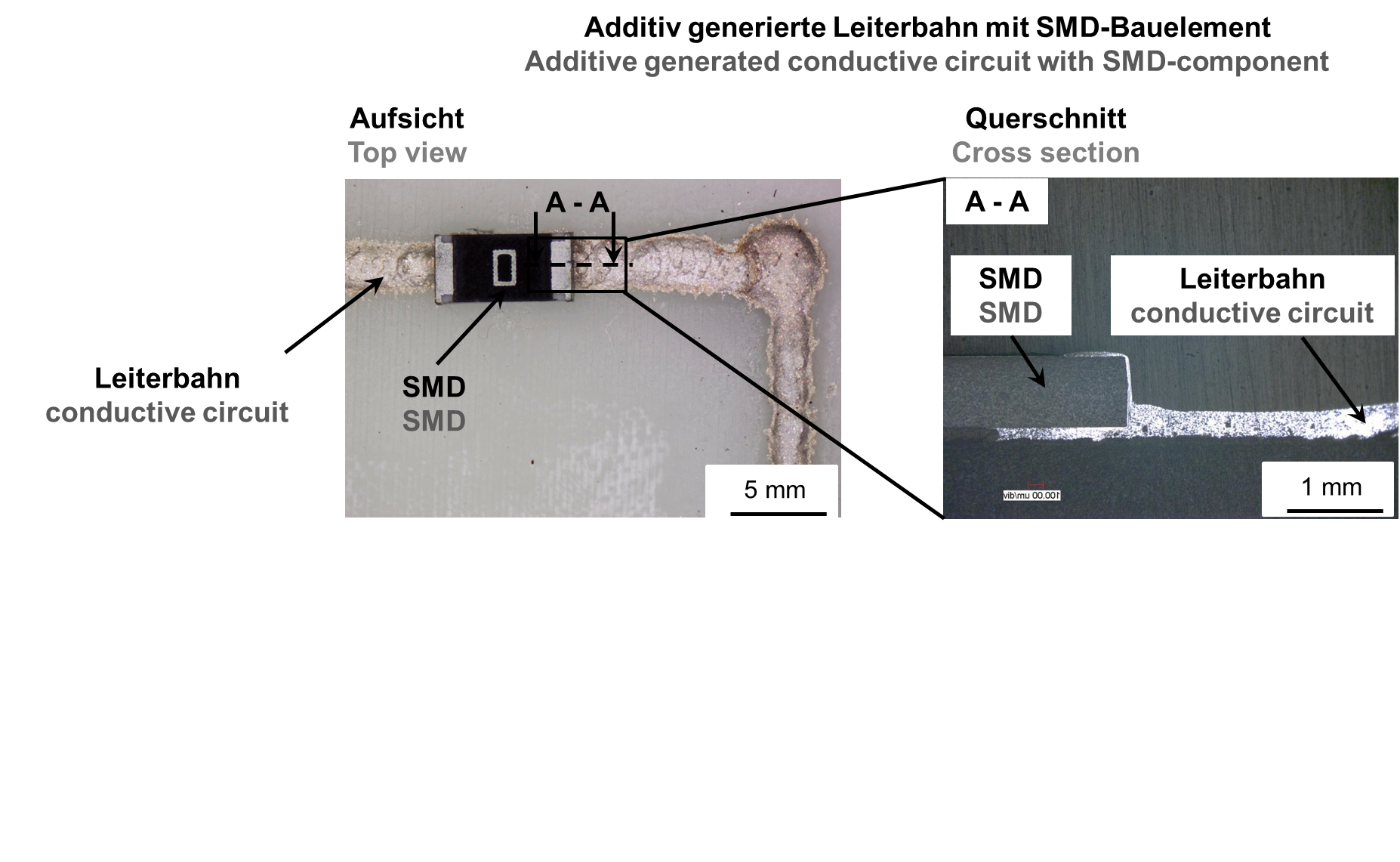

3d Printing Of Mechatronic Integrated Devices Bayerisches Laserzentrum Gmbh

Solar Panel Trina Solar Tsm 335 De06m 08 Ii 335wp Mono Secondsol

2

Asylum Seekers 13 On Vimeo

2

:quality(80)/images.vogel.de/vogelonline/bdb/449500/449554/original.jpg)

Ox1gsp05 Wsgkm

New Type Of Mems Switch Sheds New Light On Durability Electrical Engineering News And Products

Entwurf Von Impedanz Kontrollierten Leiterplatten

Hf Design Induktivitaten Kapazitaten Via Leiterbahn Mikrocontroller Net

Auto Interactive Routing To Overcome Obstacles And Other Polygons Pcb Design Blog Altium

Von Der Schaltung Zur 3d Platine Make Magazin Heise Magazine

Rogers Corporation Ro3000 Data Sheet

Enocean Ptm335c 315mhz Transmitter User Manual

Die Schaltung Und Das Platinenlayout Tinkerforge Wie Ein Prozessorboard Entsteht Golem De

No I Don T Want To Make A U Turn Guidelines For Pcb Trace Routing Blog Circuitstudio

Hauptplatine Im Computer Mit Stock Image Colourbox

Pcb Leiterbahn Routing Altium

Leiterbahnen Und Bestuckung Auch Auf Glasflachen All Electronics

Www We Online Com Web En Index Php Show Media 04 Leiterplatte 17 2 Webinar Starrflex Designfehler 1715 We Cbt Webinar Flex Rigid Design Mistakes Pdf

Led Cube 4x4x4

Development

Interactive Design And Advanced Manufacturing Of Double Solar Panel Deployment Mechanism For Cubesat Part 1 Electronics Design Request Pdf

Teilchen Photos Royalty Free Images Graphics Vectors Videos Adobe Stock

2

Www Dare Nl Images Events 19 Emc Event Presentaties 3 Signaalintegriteit Op De Pcb Victor Haagh Wurth Elektronik Pdf

Leiterbahnen Hd Stock Images Shutterstock

Reverse Engineering Target 3001 Pcb Design Freeware Is A Layout Cad Software Support Tutorials Shop

Http Dl36mmdz Cloudfront Net Uploads Eagle Resources Files 000 002 316 Original Design Checklist En Pdf

Leiterbahnen Bildburg

Strombelastbarkeit Von Leiterbahnen

Pcb Leiterbahn Routing Altium

Http Www Cadsoftusa Com Resources Documentation

Flickriver N24 Pool

Nomograph From Ipc 2221 For External Conductors 2 With Example Of Download Scientific Diagram

_computer-mikrochip-leiterbahnen-leiterplatten-platine-chip.jpg)

Prisma Schuster Computer Mikrochip Leiterbahnen Leiterplatten Art Print

Drawing Datasheet By Harting Digi Key Electronics

Meander A Track Target 3001 Pcb Design Freeware Is A Layout Cad Software Support Tutorials Shop

Easy Pcb Routing Board Layout With Altium Designer Pcb Design Blog Altium

Kicad Design Regeln Eurocircuits

Leiterbahn Youtube

Von Der Schaltung Zur 3d Platine Make Magazin Heise Magazine

Opening Windows For New Spintronic Studies Electrical Engineering News And Products

Leiterbahn Posts Facebook

Ingo Maurer 15 By Inform Interiors Issuu

Elektro Fussbodenheizung Zum Nachrusten Schwimmend 80 2w M Heizfolie Komplett

Data Transmission High Resolution Stock Photography And Images Alamy

Devre 22v 12v 5 Amper Konvetor Gif 704 987 Electronics Basics Solar Power System Amper

Der Apfeldoktor S Competitors Revenue Number Of Employees Funding Acquisitions News Owler Company Profile

Abbildung 28 Kreuzungsfreie Leiterbahnen Step1 Moglicher Download Scientific Diagram

80 Drc Error A Toolchain Issue Or A Feature Issue 17 Nitrokey Nitrokey Pro Hardware Github

Xwvjrx6zoeuynm

Pcb Designrichtlinien Grafik Strombelastbarkeit Eurocircuits

Leiterbahnen Hd Stock Images Shutterstock

Mid Baugruppen In Heisspragetechnik Hot 2e Mechatronic

Leiterbahnen Hd Stock Images Shutterstock

Customised Solutions In Electronics Development

Irlbacher Druckt Leiterbahnen Direkt Auf Glas Frontplatten Hochschule Fur Angewandte Wissenschaften Fachhochschule Landshut Pressemitteilung Pressebox

Leiterbahnen Hd Stock Images Shutterstock

Orcad Pcb Designer Professional Mit Pspice Flowcad

Computer Motherboard With Chips And Connecting Strips In Detail Stock Photo Alamy

Testaubau Slotcar Alu Leiterbahnen Youtube

Abbildung 28 Kreuzungsfreie Leiterbahnen Step1 Moglicher Download Scientific Diagram

High Speed Pcb Design Principles Keep Traces Short And Direct Altium

Glossing Von Leiterbahnen

Luca Valzania Autore A Cadlog

Leiterbahnen Hd Stock Images Shutterstock

Abstract Information Highway With Computer Stock Photos And Images Agefotostock

2

Gxp Platine Board Leiterbahnen Wasserfarbe Grun Mousepad Querformat Gxp Design Experience Life Shop

Http Dl36mmdz Cloudfront Net Uploads Eagle Resources Files 000 002 316 Original Design Checklist En Pdf

Figure 6 From Ein Tragbares Massenspektrometer In Mems Technologie A Portable Mems Based Mass Spectrometer Semantic Scholar

Flex And Rigid Flex Boards Multi Circuit Boards

Flickriver N24 Pool

Grune Leiterplatte Mit Lotpunkten Und Leiterbahnen Buy This Stock Photo And Explore Similar Images At Adobe Stock Adobe Stock

Leiterbahnen Hd Stock Images Shutterstock

Iiidaward 17 In Information Design By Hi Pe At Martin Foessleitner Issuu

Guard Traces

Enrihilft Jens Enrihilft Twitter

2

2

Push Shove Target 3001 Pcb Design Freeware Ist Eine Layout Cad Software Support Tutorials Shop

Integration Of Conductive Circuits By Embedding Stereolithography Bayerisches Laserzentrum Gmbh

Ernst Reiner Gmbh Co Kg Techpilot